How CPUs Manage Interrupt Handling

Introduction to CPU Interrupt Handling

In the realm of computer systems, the Central Processing Unit (CPU) is the brain that executes instructions and processes data. One of the critical functions of a CPU is managing interrupts, which are signals that temporarily halt the CPU’s current activities to address more urgent tasks. This article delves into how CPUs manage interrupt handling, exploring the mechanisms, types, and processes involved.

What is an Interrupt?

An interrupt is a signal sent to the CPU that indicates an event needing immediate attention. Interrupts can originate from hardware devices, software applications, or even the CPU itself. When an interrupt occurs, the CPU stops executing its current instructions and jumps to a specific routine to handle the interrupt. Once the interrupt is addressed, the CPU resumes its previous activities.

Types of Interrupts

Interrupts can be broadly categorized into two types: hardware interrupts and software interrupts.

Hardware Interrupts

Hardware interrupts are generated by external devices such as keyboards, mice, network cards, and disk drives. These interrupts signal the CPU to perform tasks like reading input data or writing output data. For example, pressing a key on the keyboard generates a hardware interrupt that tells the CPU to process the keystroke.

Software Interrupts

Software interrupts, also known as exceptions or traps, are generated by programs or the operating system. These interrupts can be used for various purposes, such as handling errors, executing system calls, or managing multitasking. For instance, a division by zero error in a program generates a software interrupt that the CPU must handle.

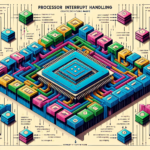

Interrupt Handling Mechanism

The process of handling interrupts involves several steps, which are managed by both hardware and software components. The key elements in this mechanism include the interrupt request (IRQ), interrupt vector table (IVT), interrupt service routine (ISR), and interrupt controller.

Interrupt Request (IRQ)

An interrupt request (IRQ) is a signal sent to the CPU by an external device or software. Each IRQ has a unique identifier that helps the CPU recognize the source of the interrupt. When an IRQ is received, the CPU acknowledges it and prepares to handle the interrupt.

Interrupt Vector Table (IVT)

The interrupt vector table (IVT) is a data structure that stores the addresses of interrupt service routines (ISRs). Each entry in the IVT corresponds to a specific IRQ and points to the ISR that handles that interrupt. When an interrupt occurs, the CPU uses the IVT to locate the appropriate ISR.

Interrupt Service Routine (ISR)

An interrupt service routine (ISR) is a special function that executes in response to an interrupt. The ISR contains the code necessary to handle the interrupt, such as reading data from a device or processing an error. Once the ISR completes its task, it signals the CPU to resume its previous activities.

Interrupt Controller

The interrupt controller is a hardware component that manages multiple IRQs and prioritizes them. It ensures that higher-priority interrupts are handled before lower-priority ones. The interrupt controller also helps the CPU identify the source of an interrupt and route it to the appropriate ISR.

Steps in Interrupt Handling

The process of handling an interrupt involves several steps, which can be summarized as follows:

- Interrupt Request: An IRQ is generated by a hardware device or software application.

- Interrupt Acknowledgment: The CPU acknowledges the IRQ and temporarily halts its current activities.

- Interrupt Vector Table Lookup: The CPU uses the IVT to locate the address of the ISR corresponding to the IRQ.

- Context Saving: The CPU saves the current state of its registers and program counter to preserve the context of the interrupted task.

- ISR Execution: The CPU jumps to the ISR and executes the code to handle the interrupt.

- Context Restoration: Once the ISR completes, the CPU restores the saved context to resume the interrupted task.

- Interrupt Completion: The CPU signals the completion of the interrupt handling process and resumes its previous activities.

Nested Interrupts and Prioritization

In complex systems, multiple interrupts can occur simultaneously or in quick succession. To manage this, CPUs support nested interrupts and prioritization.

Nested Interrupts

Nested interrupts allow the CPU to handle higher-priority interrupts even while processing a lower-priority one. When a higher-priority interrupt occurs, the CPU temporarily halts the current ISR, saves its context, and jumps to the ISR for the higher-priority interrupt. Once the higher-priority ISR completes, the CPU restores the context of the lower-priority ISR and resumes its execution.

Interrupt Prioritization

Interrupt prioritization ensures that critical tasks are addressed before less important ones. The interrupt controller assigns priority levels to each IRQ, and the CPU processes interrupts based on their priority. This mechanism helps maintain system stability and responsiveness, especially in real-time applications.

Interrupt Handling in Modern CPUs

Modern CPUs incorporate advanced features to enhance interrupt handling, such as interrupt masking, interrupt coalescing, and advanced programmable interrupt controllers (APICs).

Interrupt Masking

Interrupt masking allows the CPU to temporarily disable specific interrupts to prevent them from interfering with critical tasks. This is useful in scenarios where certain operations must not be interrupted, such as during the execution of time-sensitive code.

Interrupt Coalescing

Interrupt coalescing is a technique used to reduce the overhead of handling frequent interrupts. It involves grouping multiple interrupts into a single event, allowing the CPU to process them more efficiently. This is particularly beneficial in high-throughput systems, such as network servers.

Advanced Programmable Interrupt Controllers (APICs)

APICs are sophisticated interrupt controllers that provide enhanced features for managing interrupts in multiprocessor systems. They support advanced prioritization, routing, and masking capabilities, enabling efficient interrupt handling in complex environments.

Interrupt Handling in Operating Systems

Operating systems play a crucial role in managing interrupts and ensuring smooth system operation. They provide mechanisms for registering ISRs, handling nested interrupts, and managing interrupt priorities.

Registering ISRs

Operating systems allow device drivers and applications to register ISRs for specific IRQs. This involves associating an ISR with an entry in the IVT, enabling the CPU to locate and execute the appropriate ISR when an interrupt occurs.

Handling Nested Interrupts

Operating systems manage nested interrupts by maintaining a stack of ISRs. When a higher-priority interrupt occurs, the OS saves the context of the current ISR and pushes it onto the stack. After handling the higher-priority interrupt, the OS pops the stack to restore the context of the previous ISR.

Managing Interrupt Priorities

Operating systems provide mechanisms for setting and adjusting interrupt priorities. This ensures that critical tasks are addressed promptly, while less important tasks are deferred. The OS may also implement policies for dynamically adjusting priorities based on system load and performance requirements.

Challenges in Interrupt Handling

Despite its importance, interrupt handling presents several challenges that must be addressed to ensure efficient system operation.

Interrupt Latency

Interrupt latency refers to the time taken by the CPU to respond to an interrupt. High latency can lead to delays in processing critical tasks, affecting system performance. Minimizing interrupt latency is crucial in real-time systems, where timely response is essential.

Interrupt Overhead

Interrupt handling introduces overhead due to context switching, ISR execution, and context restoration. Excessive overhead can degrade system performance, especially in scenarios with frequent interrupts. Techniques like interrupt coalescing and efficient ISR design help mitigate this overhead.

Interrupt Storms

Interrupt storms occur when a system is overwhelmed by a high volume of interrupts, leading to excessive CPU utilization and degraded performance. Effective interrupt prioritization, masking, and coalescing techniques are essential to manage interrupt storms and maintain system stability.

FAQ

What is the difference between hardware and software interrupts?

Hardware interrupts are generated by external devices like keyboards and network cards, signaling the CPU to perform tasks such as reading input data. Software interrupts, also known as exceptions or traps, are generated by programs or the operating system to handle errors, execute system calls, or manage multitasking.

How does the CPU prioritize interrupts?

The CPU uses an interrupt controller to assign priority levels to each IRQ. Higher-priority interrupts are handled before lower-priority ones, ensuring that critical tasks are addressed promptly. Advanced programmable interrupt controllers (APICs) provide enhanced prioritization capabilities in multiprocessor systems.

What is an Interrupt Service Routine (ISR)?

An Interrupt Service Routine (ISR) is a special function that executes in response to an interrupt. The ISR contains the code necessary to handle the interrupt, such as reading data from a device or processing an error. Once the ISR completes its task, it signals the CPU to resume its previous activities.

What is interrupt latency?

Interrupt latency refers to the time taken by the CPU to respond to an interrupt. High latency can lead to delays in processing critical tasks, affecting system performance. Minimizing interrupt latency is crucial in real-time systems, where timely response is essential.

How do operating systems manage nested interrupts?

Operating systems manage nested interrupts by maintaining a stack of ISRs. When a higher-priority interrupt occurs, the OS saves the context of the current ISR and pushes it onto the stack. After handling the higher-priority interrupt, the OS pops the stack to restore the context of the previous ISR.

Conclusion

Interrupt handling is a fundamental aspect of CPU operation, enabling efficient management of tasks and ensuring system responsiveness. By understanding the mechanisms, types, and processes involved in interrupt handling, we gain insight into how CPUs maintain stability and performance in complex computing environments. As technology advances, modern CPUs and operating systems continue to evolve, incorporating sophisticated features to enhance interrupt handling and address emerging challenges.